**JULY 1976**

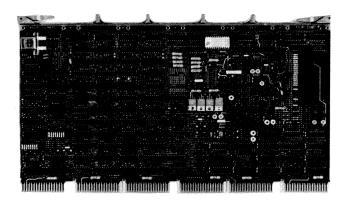

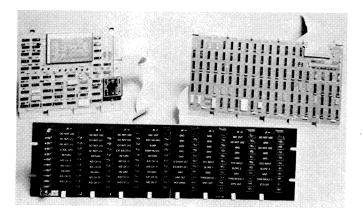

The PDP-11/03 is a complete and powerful mini-computer on four integrated circuit chips. These large-scale-integrated circuits are mounted on a single 8½ by 10½ inch printed circuit board contained within a rack mountable 3½ x 19 x 13½ inch assembly. These chips provide over 400 instructions in an addressing and I/O structure usually found only in much larger and more costly computers. Such features as hardware stack processing, eight general purpose registers, vectored interrupts and single and double operand addressing are standard.

### FEATURES:

- Small size (four LSI chips) in a convenient package

- Powerful instruction set over 400 instructions single and double operand addressing 16-bit word and 8-bit byte processing eight general purpose registers hardware stack processing

- Powerful I/O structure

vectored interrupts

priority structured I/O

LSI bus, a subset of the UNIBUS

Direct memory access for high speed peripherals

asynchronous handling of peripherals

- · Choice of solid-state or core memory

- Power-fail/auto-restart

- · Real-time clock input

### **DESCRIPTION**

### **Powerful Instruction Set**

More than 400 instructions make up the extensive instruction set. This instruction set (also used by the PDP-11/35,40) permits the user to take advantage of standard PDP-11 software. The only departure from the standard software is the addition of two new instructions, used to explicitly access the processor status word. Development programs, as in the rest of PDP-11 family, include assemblers, linkers, editors, loaders, utility packages, operating systems, and higher level languages.

**Extensive Computer Power and Small Processor Size** The processor module is built around a set of four Nchannel metal oxide semiconductor (MOS) chips, which include control and data elements as well as two microcoded read-only memories (microms). The latter are programmed to emulate the powerful PDP-11/34 instruction set, along with routines for on-line debugging techniques (ODT), operator interfacing, and boot-strap loader capability. The processor also contains a 16-bit buffered parallel input/output (I/O) bus, a 4096-word MOS random-access memory (RAM), a real-time clock input, priority interrupt control logic, power-fail/auto restart, and other features to provide stand-alone operation. The entire processor, plus all of the abovementioned features, are contained on one 8.5-by-10-inch printed circuit board.

### Modularity

The processor, memory, device interfaces, backplane, and interconnecting hardware are all modular in design. Module selection, such as the type and size of memory, and device interfaces, enable custom tailoring to meet specific application requirements. The asynchronous, bidirectional LSI-bus structures permit easy expansion of peripherals. In addition, interfaces are less complex, less costly, because addresses and data are multiplexed on the common bus.

### **Choice of Memory**

Memory modules are offered for applications requiring more storage than is available with the 4096-word MOS random-access memory on the processor board. Included are a nonvolatile 4096-word memory, a 4096-word dynamic RAM which can be automatically refreshed either by central processor microcode, or an external refresh circuit, and read-only memory (PROM/ROM) with capacity to a maximum of 4096 words in 512-word increments (2048 words in 256-word increments).

### Power-Fail/Auto Restart

Whenever DC power sequencing signals indicate an impending AC power loss, a microcoded power-fail sequence is initiated. When power is restored, the processor can automatically return to the run state. Four options are available for power up sequencing.

### Addressing

Much of the power of the processor is derived from its wide range of addressing capabilities. Processor addressing modes include sequential forward or backward addressing, address indexing, indirect addressing, 16-bit word addressing, 8-bit byte addressing, and stack addressing. Variable-length instruction formatting allows a minimum number of words to be used for each addressing mode. The result is efficient use of program storage space.

### Peripherals

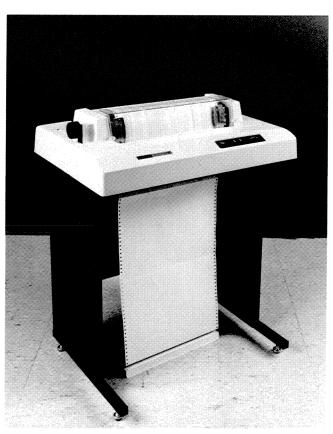

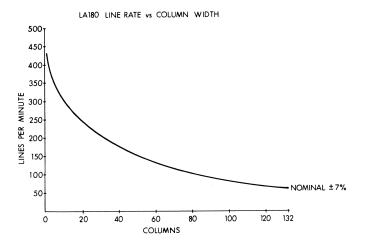

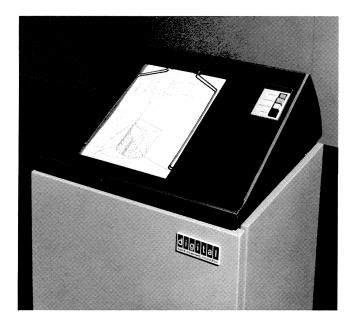

A full line of peripherals are being added to meet a wide variety of needs. These include the LA36 DECwriter terminal, the LA180 DECprinter, the RX11 floppy disk, and communications interfaces.

### Software

Software includes RT-11 real-time disk operating system, multi-user BASIC, single user BASIC, and FORTRAN.

### PDP-11/04

**JULY 1976**

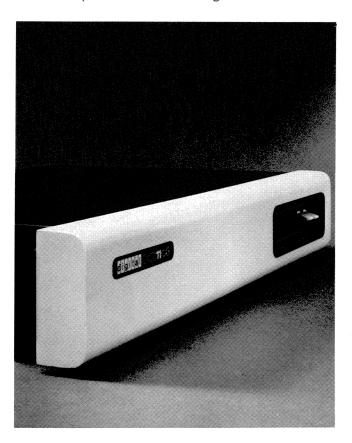

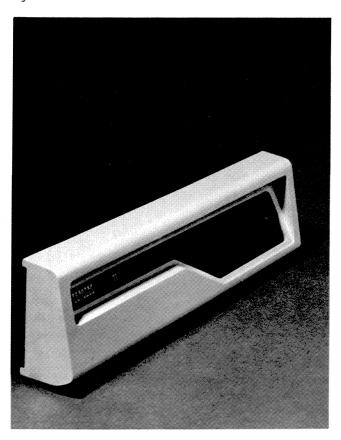

The PDP-11/04 is a low-end member of the PDP-11 family of processors with an excellent performance/price ratio. As a microprogrammed processor, the PDP-11/04 CPU is so compact that the entire CPU logic is contained on one circuit board. This provides greater flexibility during later system expansion by making additional chassis space available.

A number of "large system" features incorporated into the PDP-11/04 CPU as standard options increase its capabilities beyond those found in other computers in its class, and provide considerable flexibility in the use, maintenance, and expandability of any PDP-11/04 based system.

### FEATURES:

- Self-test diagnostic routines which are automatically executed every time the processor is powered up, the console emulator routine is initiated, or the bootstrap routine is initiated.

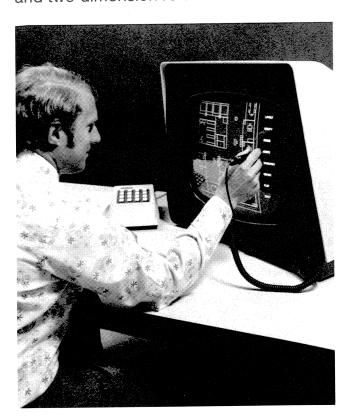

- Operator front panel with built-in CPU console emulator that allows control from any ASCII terminal without the need for the conventional front panel with display lights and switches.

- Automatic bootstrap loader which allows system restart from a variety of peripheral devices without manual switch toggling or key-pad operations.

- Choice of core or MOS memory, with parity memory optional.

- Choice of 5¼ inch or 10½ inch high mounting chassis.

### DESCRIPTION

### **CPU Console Emulator**

The "CPU Console Emulator" feature permits control of the PDP-11/04 from any ASCII terminal connected to the processor. Console emulator operations include the normal memory LOAD, EXAMINE and DEPOSIT, in addition to START or BOOT.

### **Automatic Bootstrap Loader**

To simplify program loading whenever the system is "brought up" or reloaded, an automatic bootstrap loader is included with the PDP-11/04 processor.

### **Automatic Self-Test Feature**

To assure the viability and performance readiness of the PDP-11/04 processor, a multi-function CPU test routine has been incorporated into the processor's bootstrap ROM. It is invoked every time upon initiation of the console emulator routine, and when the system is loaded with the automatic bootstrap loader, to guarantee that the basic instruction set, the internal data paths, and the lower 28K words of memory are in operational condition.

# Maintenance Feature in Optional Programmer's Console

As another step towards greater reliability and serviceability of PDP-11/04 based systems, the 11/04 includes a maintenance feature which aids in system error diagnosis. When in maintenance mode, the CPU's microcode can be single-stepped, and UNIBUS addresses as well as data can be displayed with the optional programmer's console.

The 11/04 also includes the following big computer features which are part of the PDP-11 architecture.

### Powerful instruction set

The comprehensive instruction set and addressing modes (yielding over 400 commands) offer the programming flexibility of a large computer in a 16-bit mainframe. The set provides many extra commands, so that a single instruction frequently suffices where several may be required in a traditional computer. For example, a Bit Test Instruction (BIT) can test any bit or combination of bits to determine their state.

Bit, byte and word addressing in both single- and double-operand formats make memory saving possible and simplify the implementation of control and communications applications.

Instructions make use of the processor's eight generalpurpose registers, eight addressing modes, and operate on both words and bytes—making these processors ideal for data communications applications.

#### Powerful I/O structure

A key factor of the PDP-11 Family's success is that all system elements—processor, memory, peripherals—plug into a single asynchronous high-speed bus, which transfers all addresses and data. Known as the UNIBUS, this bidirectional bus enables easy interfacing and simplifies the construction of multiprocessor or shared peripheral configurations.

The UNIBUS prevents PDP-11 systems from becoming obsolete. Because it is asynchronous, the UNIBUS is compatible with devices that operate over a wide range of speeds. Faster devices or memory can always replace older versions without affecting the system.

Through the UNIBUS, fast devices have easy directmemory access, requiring no multiplexers or synchronous DMA hardware. These devices can send, receive or exchange data without processor intervention and without intermediate buffering in memory.

The interrupt system for the PDP-11 is another departure in small-computer technology. With fully-vectored interrupts, the system eliminates the high-overhead software that determines the device service routine and code necessary to save system status. The multilevel hardware interrupt system is a standard PDP-11 feature, not an extra-cost option.

PDP-11 minicomputer systems consist of four priority levels, each of which can handle an almost unlimited number of devices. The priority of the device is a function of the device's physical location—the closer to the processor the higher its priority on that level.

The priority system makes excellent use of the PDP-11's hardware stacks. When the processor services an interrupt, it first saves important program information on the stack. This information enables the processor to automatically return to the same point in the program and the same conditions, once the current interrupt(s) has been serviced.

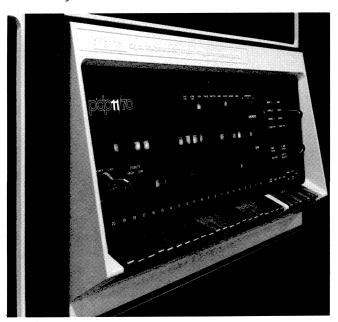

### PDP-11/34

**JULY 1976**

The PDP-11/34 is a midrange member of the PDP-11 family of processors with an excellent performance/price ratio. As a microprogrammed processor, the PDP-11/34 CPU is so compact that the entire CPU logic is contained on two circuit boards. This provides greater flexibility during later system expansion by making additional chassis space available.

A number of "large system" features incorporated into the PDP-11/34 CPU as standard options increase its capabilities beyond those found in other computers in its class, and provide considerable flexibility in the use, maintenance, and expandability of any PDP-11/34 based system.

#### FEATURES:

- Integral memory management hardware that provides program protection, memory relocation and addressing of up to 124K 16-bit words.

- Integral extended instruction set (EIS) that provides hardware fixed-point arithmetic in double-precision mode (32-bit operands).

- Self-test diagnostic routines which are automatically executed every time the processor is powered up, the console emulator routine is initiated, or the bootstrap routine is initiated

- Operator front panel with built-in CPU console emulator that allows control from any ASCII terminal without the need for the conventional front panel with display lights and switches.

- Automatic bootstrap loader which allows system restart from a variety of peripheral devices without manual switch toggling of key-pad operations.

- Choice of core or MOS parity memory.

- Choice of 51/4 inch or 101/2 inch high mounting chassis **DESCRIPTION**

### **Memory Management and User Protection**

The PDP-11/34's integral memory management facility allows a 16-bit machine to provide 18-bit capability for a sizeable extension of addressable memory. Through this facility, system memory can be expanded from its basic 28K words to a maximum of 124K words, more than 4 times its normal memory capacity.

The user has access to this memory in up to 32K units through 8 programmable registers. These registers assign (or map) the user's virtual addresses, in 4K pages, to 4K physical addresses anywhere within core memory. The starting address of each 4K physical segment is stored in the registers.

The user need only provide virtual addresses; transformation to physical addresses takes place automatically and transparently.

Memory management provides two additional features useful especially in a multi-user environment:

- Memory protection, which can be invoked by designating selected memory segments as "no access" or "read only" areas.

- Selective swapping, which prevents the unnecessary swapping (out) of memory segments not modified while memory resident, making swapping of user programs more efficient.

#### **CPU Console Emulator**

The "CPU Console Emulator" feature permits control of the PDP-11/34 from any ASCII terminal connected to the processor. Console emulator operations include the normal memory LOAD, EXAMINE and DEPOSIT, in addition to START or BOOT.

### **Automatic Bootstrap Loader**

To simplify program loading whenever the system is "brought up" or reloaded, an automatic bootstrap loader is included with the PDP-11/34 processor.

#### **Automatic Self-Test Feature**

To assure the viability and performance readiness of the PDP-11/34 processor, a multi-function CPU test routine has been incorporated into the processor's microcode and bootstrap ROM. It is invoked every time the processor initiates a power up sequence, upon initiation of the console emulator routine, and when the system is loaded with the automatic bootstrap loader, to guarantee that the basic instruction set, the internal data paths, and the lower 28K words of memory are in operational condition.

## Maintenance Feature in Optional Programmer's Console

As another step towards greater reliability and serviceability of PDP-11/34 based systems, the 11/34 includes a maintenance feature which aids in system error diagnosis. When in maintenance mode, the CPU's microcode can be single-stepped, and UNIBUS addresses as well as data can be displayed with the optional programmer's console.

The 11/34 also includes the following big computer features which are part of the PDP-11 architecture.

### Powerful instruction set

The comprehensive instruction set and addressing modes (yielding over 400 commands) offer the programming flexibility of a large computer in a 16-bit mainframe. The set provides many extra commands, so that a single instruction frequently suffices where several may be required in a traditional computer. For example, a Bit Test Instruction (BIT) can test any bit or combination of bits to determine their state.

Bit, byte and word addressing in both single- and double-operand formats make memory saving possible and simplify the implementation of control and communications applications.

Instructions make use of the processor's eight generalpurpose registers, eight addressing modes, and operate on both words and bytes—making these processors ideal for data communications applications.

#### Powerful I/O structure

A key factor of the PDP-11 family's success is that all system elements—processor, memory, peripherals—plug into a single asynchronous high-speed bus, which transfers all addresses and data. Known as the UNIBUS, this bidirectional bus enables easy interfacing and simplifies the construction of multiprocessor or shared peripheral configurations.

The UNIBUS prevents PDP-11 systems from becoming obsolete. Because it is asynchronous, the UNIBUS is compatible with devices that operate over a wide range of speeds. Faster devices or memory can always replace older versions without affecting the system.

Through the UNIBUS, fast devices have easy directmemory access, requiring no multiplexors of synchronous DMA hardware. These devices can send, receive or exchange data without processor intervention and without intermediate buffering in memory.

The interrupt system for the PDP-11 is another departure in small-computer technology. With fully-vectored interrupts, the system eliminates the high-overhead software that determines the device service routine and code necessary to save system status. The multilevel hardware interrupt system is a standard PDP-11 feature, not an extra-cost option.

PDP-11 minicomputer systems consist of four priority levels, each of which can handle an almost unlimited number of devices. The priority of the device is a function of the device's physical location—the closer to the processor the higher its priority on that level.

The priority system makes excellent use of the PDP-11's hardware stacks. When the processor services an interrupt, it first saves important program information on the stack. This information enables the processor to automatically return to the same point in the program and the same conditions, once the current interrupt(s) has been serviced.

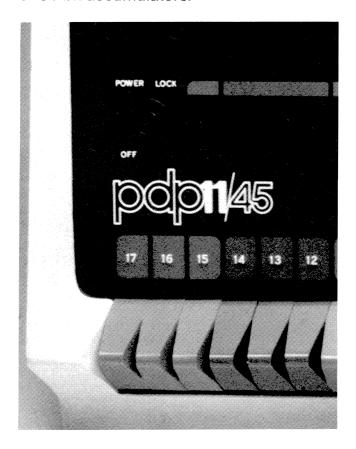

**JULY 1976**

The PDP-11 is optimized for speed. The extremely high-speed CPU circuits allow program execution speeds in excess of three million instructions per second. The memory systems are just as state-ofthe-art. Bipolar memory is available at a speed of 300 nanoseconds. Core memory is available at a speed of 980 nanoseconds. They may be combined on a single system up to a total of 32K bipolar and core to 128K. High speed computations are performed by an independent floating point processor. It overlaps its operations with that of the central processor and offers average double precision multiply times of 5.43 microseconds, working right within its own set of 64-bit accumulators.

### **FEATURES:**

- Memory expandable to 256K bytes.

- Memory segmentation, protection and relocation.

- Option FP11-C floating point processor with advanced features and operation with 32-bit and 64-bit numbers.

- · Reliable core memory.

- Fast secondary bus between processor and solid-state memory which operates in parallel with the UNIBUS.

### DESCRIPTION

The PDP-11/45 also includes the following big computer features:

### Powerful instruction set

The comprehensive instruction set and addressing modes (yielding over 400 commands) offer the programming flexibility of a large computer in a 16-bit mainframe. The set provides many extra commands, so that a single instruction frequently suffices where several may be required in a traditional computer. For example, a Bit Text Instruction (BIT) can test any bit or combination of bits to determine their state.

Bit, byte and word addressing in both single- and double-operand formats make memory saving possible and simplify the implementation of control and communications applications.

Instructions make use of the processor's eight generalpurpose registers, eight addressing modes, and operate on both words and bytes—making these processors ideal for data communications applications.

### Powerful I/O structure

A key factor of the PDP-11 Family's success is that all system elements—processor, memory, peripherals—plug into a single asynchronous high-speed bus, which transfers all addresses and data. Known as the UNIBUS, this bidirectional bus enables easy interfacing and simplifies the construction of multiprocessor or shared peripheral configurations.

The UNIBUS prevents PDP-11 systems from becoming obsolete. Because it is asynchronous, the UNIBUS is compatible with devices that operate over a wide range of speeds. Faster devices or memory can always replace older versions without affecting the system.

Through the UNIBUS, fast devices have easy directmemory access, requiring no multiplexers or synchronous DMA hardware. These devices can send, receive or exchange data without processor intervention and without intermediate buffering in memory. The interrupt system for the PDP-11 is another departure in small-computer technology. With fully-vectored interrupts, the system eliminates the high-overhead software that determines the device service routine and code necessary to save system status. The multi-level hardware interrupt system is a standard PDP-11 feature, not an extra-cost option.

PDP-11 minicomputer systems consist of four priority levels, each of which can handle an almost unlimited number of devices. The priority of the device is a function of the device's physical location—the closer to the processor the higher its priority on that level.

The priority system makes excellent use of the PDP-11's hardware stacks. When the processor services an interrupt, it first saves important program information on the stack. This information enables the processor to automatically return to the same point in the program and the same conditions, once the current interrupt(s) has been serviced.

**JULY 1976**

Overlapped operations and high speed components are responsible for the high performance of the 11/55. It takes full advantage of such advanced components as dual ported bipolar memory, a high speed double precision floating point processor, and hardware memory management.

### **FEATURES**

### **High Speed Components**

- 300 nanosecond, dual-ported bipolar memory

- High speed floating point processor with 46 hardwired instructions

- Internal micro-instruction cycle time of 150 nanoseconds

- Instruction execution time of 300 nanoseconds

### **Overlapped Operations**

- Instruction pipelining allows the fetch of the next program instruction to be overlapped with the instruction currently in execution

- Floating point calculation can be performed independent of central processor operations, freeing the CPU to simultaneously perform nonfloating point computations.

- Dual bus structure allows direct memory access without cycle stealing on the UNIBUS

### Scope

- Up to 256K bytes of combined bipolar and core memory (up to 64K bytes bipolar alone)

- Three CPU operating modes (kernal, supervisor, and user) which enhance system operating efficiency and program protection.

- Hardware memory management, with three sets of memory management registers—one set per CPU operating mode.

- Two sets of eight general purpose registers which, coupled with three CPU operating modes, eliminate the need for saving register contents in a real-time applications environment.

- · Direct memory access

- · Power fail/auto restart

### **DESCRIPTION**

### "LARGE SYSTEM" FEATURES

### **Extensive Instruction Set**

The PDP-11's comprehensive instruction set offers the programming flexibility of a large computer in a 16-bit mainframe. The set provides unusual but often required instructions, so that a single instruction frequently suffices where several may be required in a traditional machine. For example, a bit test instruction (BIT) can test any bit or combination of bits to determine their state. In a conventional machine, this task would require several masking operations.

Bit, byte and word addressing in both single and double operand formats make efficient use of memory and simplify the implementation of control and communications applications.

PDP-11 double operand instructions allow a programmer to perform several operations with a single instruction. For example, ADD A,B adds the contents of location A to location B and stores the result in location B. Three instructions would be necessary with the traditional instruction set:

#### PDP-11

ADD A,B: Add contents of location A to location B and store results in location B.

#### Conventional

LDA A: Load contents of location A into accumulator. ADD B: Add contents of location B into accumulator. STA B: Store result in location B.

Due to the UNIBUS, the PDP-11 does not require I/O instructions; the same instruction that performs a register-to-register transfer performs a memory-to-device register transfer or a memory-to-memory transfer. In the double operand instruction ADD A,B therefore, A and B can be registers, a register and a memory location, or two memory locations.

The instruction set contains a full set of conditional branches, eliminating excessive use of "jump" instructions. A branch is also included for overflow of a signed integer. Many computers over-economize and eliminate this branch, thereby requiring a 5 to 8 instruction subroutine. All instructions can directly address the 28K word memory space.

### **General Registers**

There is no single accumulator in the PDP-11; instead, there are 8 general registers that can function as accumulators. In addition, they can be used to specify addresses in a variety of ways. Arithmetic operations between general registers is the simplest from a programming standpoint, and the fastest from a timing standpoint. It is advantageous to use them for operating on frequently accessed data. The general registers can be used to:

- Hold data.

- Point to an address that contains data (indirect or deferred addressing).

- Point to an address, which in turn points to an address that then contains data (2 levels of indirect addressing).

- Contain an (indirect) address which, following use for indirect addressing, is automatically incremented to the next higher address.

- Point to one address; then be automatically decremented to point to the next lower address, before being used.

- Hold the offset number for forming an effective address (adding an offset to a base address).

The architecture of the PDP-11 actually allows any memory location to act like an accumulator (or pointer). The general registers are the only ones that are used for automatic incrementing or decrementing and direct offset addressing.

### Hardware Interrupts

The interrupt system for the PDP-11 is another feature generally found only in large computer technology. With fully vectored interrupts, the system eliminates the high overhead software that determines which device service routine to use and the code necessary to save system status. In addition, the multi-level hardware interrupt system is a standard PDP-11 feature, not an extra cost option.

The PDP-11 system consists of four priority levels, each of which can handle an almost unlimited number of devices. The sub-priority of the device is a function of the device's physical position—the closer to the processor, the higher its sub-priority on that level.

The device causing an interrupt provides a direct vector to its own service routine, eliminating the slow and tedious operation of polling all devices to see which one interrupted.

The device also provides status information for its own service routine. Thus the programmer has the flexibility of assigning a device to a higher priority and its service routine to another priority without writing special software.

The system also allows interrupts to be enabled or disabled, through software, during program operation. Such masking allows priorities to change dynamically in response to system conditions. For example, a real-time program can disable data entry terminals whenever critical analog data is being collected. As soon as the scan is complete, the terminals can be automatically enabled and ready to input data.

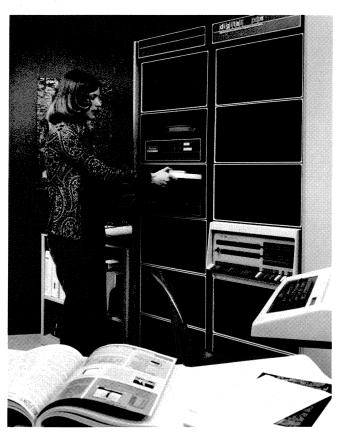

### PDP-11/70

**JULY 1976**

The PDP-11/70 is the most powerful computer in the PDP-11 family. It provides high system throughput in a multi-user, multi-tasking environment requiring large amounts of additional memory; fast response for high performance time-sharing; and computational power for high-speed real-time applications. It is the systems level PDP-11 that combines high throughput with expandability and reliability.

### **FEATURES**

### Throughput

- Cache memory organization to provide very fast program execution speed and high system throughput

- 5.8 megabyte I/O bandwidth

- Optional high-speed, mass storage controllers an an integral part of the CPU, to provide dedicated 32-bit paths to high performance storage devices

- Optional high speed floating point processor with 46 hard-wired instructions and operation with 32-bit and 64-bit numbers

- Memory management for relocation and protection in multi-user, multi-task environments

- Fail soft cache memory

- Sophisticated diagnostics

### Expandability

- Ability to access up to 4 million bytes of main memory Reliability

- Extensive parity checking

### Compatibility

UNIBUS for compatibility with the rest of the PDP-11 family

### DESCRIPTION

High throughput is comprised of two things—individual component speed and a system organization which efficiently integrates these components. For example, the high speed 11/70 floating-point processor can completely overlap the CPU instruction cycles. The PDP-11/70 is designed for speed, with the power and flexibility to translate processor speed and 32-bit I/O architecture into high system throughput.

### Instruction Speed

The PDP-11/70 CPU utilizes high-speed TTL (Schottky) logic pioneered in our PDP-11/45. The circuitry yields a basic execution time of just under 300 nanoseconds. This means, for example, that adding two integers in registers can be performed with one instruction (ADD R0, R1) in just 300 nanoseconds. Internal buffering allows the fetch of the next program instruction to be overlapped with execution of the current instruction.

#### Cache

An integral cache memory is a standard feature of every PDP-11/70. The cache is a high-speed bipolar memory with a 2,048-byte capacity. It has a cycle time of only 240 nanoseconds. The cache acts like a buffer between the CPU registers and main (core) memory. Whenever a request is made to fetch data from memory, the circuitry checks to see if the data is already in cache. If it is, it is fetched from cache, and no main memory read is required. If not in cache, four bytes are transferred in parallel from main memory for execution. When a request is made to write data into main memory, it is written both into the cache and main memory. This assures that main memory always has the most up-to-date data.

### 32-Bit Internal Data Paths

To facilitate the transfer of data in and out of the cache memory, the PDP-11/70 utilizes high-speed 32-bit data paths. These internal busses transfer 32 bits (and four parity bits—one per byte) in parallel. Thus, one request can transfer four bytes of data between main memory and cache, or four bytes of data between a high-speed peripheral controller and main memory at directmemory-access speeds.

Consequently, the high-speed peripheral bus provides up to 5.8 MB/sec band width for high performance peripherals.

### **Integrated Mass Storage Controllers**

The integrated mass bus controllers are high-speed mass storage controllers. They interface devices such as the RP04, RP05 and RP06 disk packs, RS03 and RS04 swapping disks, and the TU16 magnetic tapes to the 32-bit internal data paths. The controllers have been designed to provide high throughput by such features as:

- All controllers can transfer data simultaneously since each controller is connected to the memory system with its own built-in data path.

- While one device on a controller is transferring data, control operations such as seek or rewind may be issued to another device on the same controller. The operation can be initiated and an interrupt generated when it is complete.

### **Floating-Point Processor**

Based on its own set of six 64-bit floating-point accumulators, and 46 additional instructions, the PDP-11/70's floating-point processor carries out high-speed calculations in either single precision (32 bits) or double precision (64 bits).

The basic add, subtract, multiply, divide instructions are complemented by a whole range of additional hardware instructions. Floating-Point Clear, Negate, and Make Absolute instructions allow direct operation on values stored in memory. The Test and Compare instructions allow direct testing for plus, minus, zero, greater than, less than, and equal to. The Convert instructions allow integers (16-bit or 32-bit) to be converted to floating point and loaded into floating accumulators, all in a single operation. These additional instructions allow for faster, more compact coding of computation routines.

Fast as it is, the floating-point processor can give even faster effective computation speeds by taking advantage of overlap. Since the floating-point processor is a separate processor it can operate independently of the central processor. Therefore, during the actual computation time involved in a floating-point operation, the central processor can proceed to execute nonfloating instructions. In many cases floating-point execution time is 100 percent overlapped with CPU operation. The overlapped operation also leaves the CPU free to respond to interrupts, so the use of the floating-point unit does not affect the worst-case response to interrupts in real-time applications. Four factors combine to provide the exceptional computation speed of the PDP-11/70 floating-point processor: fast circuitry, large instruction set, multipleaccumulator architecture, and overlapped operation.

### Memory

The PDP-11/70 memory system was designed to meet four criteria. It must provide for very fast data transfer to and from the CPU; it must provide for large capacity and easy expansion; it must provide high reliability and error diagnosis; and it must be cost effective. To provide these functions, the PDP-11/70 memory system utilizes an integral cache memory at 32-bit access for speed, core memory for large-scale capacity, easy expansion, nonvolatility, and cost effectiveness; it also incorporates byte parity and bad block mapping for reliability. Main memory is composed of core memory modules that are byte addressable and expandable in 64K or 128K-byte increments to a system capacity of just over 4 million bytes. Proven core memory is used to provide maximum price/performance benefits for the system.

### **Memory Management**

The PDP-11/70 memory management unit provides the hardware facilities necessary for complete memory management and protection without any time overhead. It is a memory management facility for accessing all of physical memory and for multi-user, multi-programming systems where memory protection and relocation facilities are necessary.

In order to most effectively utilize the power and efficiency of the PDP-11/70 in medium and large scale systems it is necessary to run several programs simultaneously. In such multi-programming environments several user programs would be resident in memory at any given time. The task of the supervisory program would be: to control the execution of the various user programs, manage the allocation of memory and peripheral device resources, and safeguard the integrity of the system as a whole by careful control of each user program.

In a multi-programming system, the memory management unit provides the means for assigning memory pages to a user program and preventing that user from making any unauthorized access to these pages outside his assigned area. Thus, a user can effectively be prevented from accidental or willful destruction of any other user program or the system executive program.

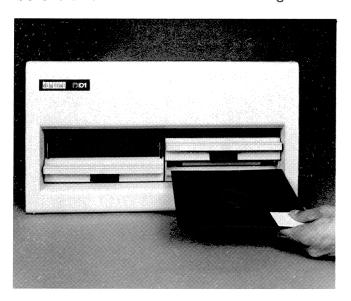

# **RX11 Floppy Disk System**

**JULY 1976**

The RX11 Floppy Disk System is a highly reliable, low-cost, mass storage subsystem, capable of storing up to 256,256 8-bit bytes per drive in an industry-compatible format. The RX11 provides a compact data interchange and software distribution medium for critical I/O applications. In addition, the RX11's random-access capability allows configuring very low-cost, disk-based systems with small PDP-11 processors. Such systems can satisfy the needs of applications that could never before afford random access storage.

### **FEATURES**

### Speed

- 18 microseconds per byte transferred

- 83 milliseconds average latency

- 483 milliseconds average access

- 30 seconds to read the whole diskette

### Capacity

- 256K 8-bit bytes/diskette

- 2 drives/controller

### **Human Engineering**

- Extremely simple to load-just insert

- Small and compact—easy to transport or mail

- Preformatted

### Reliability

- Simple construction and microprogrammed controller reduce complexity

- Long disk life because head contacts disk only during read/write

- Cyclic redundancy check, longitudinal redundancy check, and parity

### Other

Industry standard preformatting facilitates interchangeability and lowers hardware costs.

### DESCRIPTION

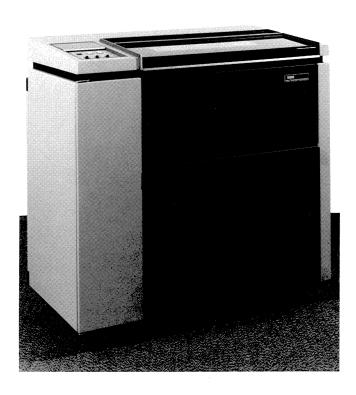

The RX11 floppy disk system consists of an RX01 floppy disk drive unit an a PDP-11 quad interface module which requires a single SPC slot. The RX01 includes either one or two drives, a microprogrammed controller module, and a read/write electronics module, all housed in a 10½ inch, rack-mountable chassis. Up to two drives can be supported by each controller for a total storage capacity of 512,512 bytes.

Given an absolute sector address, the RX01 locates the desired sector and performs the indicated function. It automatically verifies head position and generates and verifies the cyclic redundancy check (CRC) character.

Track-to-track moves require ten milliseconds for the move plus twenty milliseconds for settling time if the head is loaded for a read or write. The rotational speed of the diskette is 360 rpm, which results in an average latency time of 83 milliseconds. The track-to-track move, head settling, and latency time produce an average access time of 483 milliseconds. During a sequential access, the whole diskette can be read in about thirty seconds.

### The Media

The RX01 floppy disk uses the industry-standard "diskette" or "floppy" media, which are thin, flexible oxide-coated disks similar in size to a 45-rpm phonograph record. The disk is recorded on one side only and is permanently contained in an 8-inch square, flexible envelope.

The envelope has a large center hole for the drive spindle, a small hole for track index sensing, and a large slit for the read/write head. A solenoid contact load pad is located on the opposite side of the envelope. The inside of the envelope is covered with a soft material, designed to wipe the disk surface clean just before reading.

The diskette contains 77 tracks and 26 sectors per track. Each sector can store 128 8-bit bytes for a total formatted capacity of 256,256 8-bit bytes.

The diskette is an ideal storage, interchange, and software distribution medium. Compared to disk cartridges or disk packs, it is very inexpensive. Because it is flat and thin, the diskette is compact, enabling large amounts of data to be conveniently stored in a small space. Diskettes can also be easily transported in a briefcase or in a manila envelope.

The diskette is preformatted in the industry-standard format. However, the file structure is software dependent and may vary from system to system. Preformatted diskettes also reduce hardware costs by eliminating the circuitry required to generate the correct format.

### Reliability

The RX01 provides exceptional reliability as well as low cost. The simple mechanical construction of the drive and the use of a microprogrammed controller that reduces hardware complexity contribute to reliability. To enhance disk life, the head contacts the disk only during reading or writing. With the head loaded on a given track, the media can withstand one million passes.

The RX01 performs parity checks and provides error indications. Each sector has a cyclic redundancy check (CRC) character as part of the header field, and another CRC character as part of the data field. The RX01 generates and verifies the CRC characters and provides error indications.

| RX11           |

|----------------|

| floppy         |

| 256K           |

| 2              |

|                |

| 512K           |

| 483 ms         |

| <b>36</b> μsec |

|                |

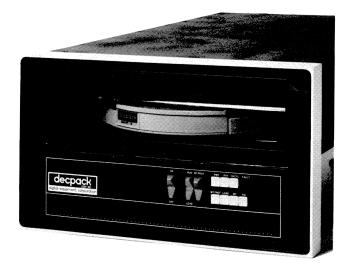

# RK05 DECpack

**JULY 1976**

The RK05 family is DIGITAL's entry level, low cost, disk storage system for PDP-11 computers. The family consists of a controller, a 2.5 MB RK05J disk drive with removable cartridges and a 5MB FK05F non-removable media disk drive. The RK05 family is completely supported by RT11, RSX-11M, RSX-11D, RSTS/E, IAS and MUMPS-11 operating systems.

DIGITAL's rugged and field proven RK05 is the most successful disk product in the minicomputer industry; worldwide, DIGITAL has installed over 20,000 drives.

### **FEATURES**

### Speed

- Fast access

- Overlapped seeks for high throughput

Capacity

- 2.5 to 20 million bytes on-line storage per controller

- RK05J with removable cartridges for virtually unlimited off-line storage

- RK05F for economical on-line storage

### **Human Engineering**

- Easy copying from disk to disk

- · Easy cartridge handling

### Reliability

- Dust protection

- Accurate positioning

- Transfer verification

- Self-contained power supply

- Environment 50°-104° F

#### DESCRIPTION

The RK05 is a 2.5 megabyte disk drive with removable cartridges. Cartridges recorded on one RK05J can be read on another RK05J and vice-versa. The RK05F is a 5 megabyte non-removable media disk drive. The RK05F is essentially identical to the RK05J except that it has twice the storage capacity, achieved by doubling the track density.

The RK05F has been designed to appear to a controller as if there were two "logical" RK05J drives connected to it. This design feature permits RK05J and RK05F drives to co-exist on the controller for all PDP-11 computer systems. More importantly, the RK05J and RK05F drives are fully compatible in terms of software, diagnostics and programs.

The dual drive disk subsystem consisting of an RK05J and an RK05F with 2.5 MB of removable storage and 5 MB of non-removable storage is an attractive mass storage system. The RK05J, which must always be the first drive on a controller, allows unlimited off-line storage, while the RK05F offers economical on-line storage. Programs and operating systems can be easily loaded on an RK05F or backed up for off-line storage via the RK05J.

Dual drive systems, either RK05J/RK05F or 2 RK05Js, have two independent positioners which allow fast copying of information from one disk to another. In dual drive configurations, the computer system remains operational while removable cartridges are being changed.

The sophisticated controller can overlap seeks on multi-drive systems. While one drive is performing a read or write operation, other drives can be seeking new track locations. Overlapped seeks are currently supported by RSX-11D, RSTS/E and IAS on all RK05J systems but not on mixed RK05J/RK05F systems.

As storage requirements increase, additional capacity can be added via either RK05J or RK05F drives. Existing computer systems which already have a PDP-11 controller (RK11D/RK11C) and an RK05J can be economically upgraded via the RK05F. The RK05F's design eliminates the need for time consuming and extremely expensive program conversions.

The RK05F utilizes two drive positions on a controller instead of the single position utilized by an RK05J. The RK05F is restricted to positions (0,1), (2,3), (4,5), (6,7) on a controller. There must be at least one RK05J drive on a controller and therefore the maximum system configurations (20 MB) for a PDP-11 controller (8 positions) will be 8 RK05J, 2 RK05J/3RK05F, 4 RK05J/2RK05F, etc.

|                                               | RK05F               | RK05J               |

|-----------------------------------------------|---------------------|---------------------|

| Capacity                                      | 5MB                 | 2.5 MB              |

| Media                                         | Non-removable       | Removable cartridge |

| BPI/TPI                                       | 2200/200            | 2200/100            |

| Data Rate                                     | 180 KB/sec          | 180 KB/sec          |

| Average Latency                               | 20 msec             | 20 msec             |

| Positioning time<br>track-to-track<br>average | 8.5 msec<br>56 msec | 10 msec<br>50 msec  |

| Dimension                                     | 19"x26.5"x10.5"     | 19"x26.5"x10.5"     |

|                                               |                     |                     |

# RP04/05/06 Disk Pack Subsystem

**JULY 1976**

The RP04, RP05, and RP06 disk drives are high capacity, high performance disk drives. Each drive, when coupled with a processor-specific controller, becomes a disk subsystem. The feature sheet describes the three drives, and the two subsystems using them.

### **FEATURES**

### Speed

- 28 milliseconds average seek

- 1.24 microsecond per byte peak transfer

- Overlapped seeks

- Direct memory access

- · Dual access option

### Capacity

- 100 million or 200 million 8 bit bytes/disk pack (unformatted)

- 1.6 billion 8 bit bytes/controller maximum

### **Human Engineering**

On-line pack formatting

### Reliability

- · Error detection, logging and correction

- Extensive diagnostic software support

- Parity checking on all data and control transfers between controller and disk drive

- Offset positioning

### DESCRIPTION

### **Disk Drive Description**

The RP04 and RP05 are 100 million byte disk drives. The RP06 disk drive has double the capacity of the RP04 and RP05, or 200 million bytes. The RP05 is field upgradable to an RP06: the high track density of the RP06 requires different media, read/write circuitry, and heads.

All three drives function identically. Average access time is 36 milliseconds, which includes the time for head positioning and rotational latency. The peak transfer rate is 806,000 bytes per second.

The disk drive is designed for reliability. A phase-lock-loop clock system and modified frequency modulation (MFM) recording offer the latest in reliable reading and recording techniques. Error detection and correction hardware in each drive provides an error correction code (ECC) for correcting any error burst of up to 11 consecutive bits within a 256-byte data field. Software can correct these data field errors without rereading the disk.

Program controlled head offset positioning corrects for slight mechanical misalignment between the heads and the disk pack; the head can be moved about the track centerline in incremental steps. This feature virtually guarantees that packs can be transported between different drives.

To further increase data integrity, the drive has a hardware write-check capability and verification of sector, track, and cylinder positioning. Built-in registers for disk data path checkout simplify maintenance. Both the RP04 and RP05 use the same disk pack so that packs written on one type of drive can be read on the other. The RP06 uses a newly developed pack which is RP06 specific.

The RP05 and RP06 drives have removable logical address units, which plug into the front of the drive to simplify subsystem reconfiguration.

### **Disk Subsystem Description**

The RP04/05/06 disk drives use the same controllers and can be intermixed.

There are two disk subsystems:

- RP04/05/06 for all UNIBUS PDP-11 systems except the PDP-11/70

- RWP04/05/06 for the PDP-11/70

All subsystems are expandable to eight disk pack drives or 800 million bytes for RP04 and RP05 subsystems, and 1600 million bytes for RP06 subsystems. The removable disk pack offers the flexibility of unlimited off-line storage. All subsystems transfer at the same speed (1.24 microseconds per byte max).

On multi-drive systems, positioning operations can be overlapped for efficiency. While one drive is reading or writing, one or more other drives can be positioning to a new cylinder for the next transfer.

Parity checking is done on both data and control information transfers for increased reliability. The controller also detects and flags memory parity errors. The disk system interrupts the processor on command completion and on error conditions. Extensive error indicators allow on-line diagnostics, and status indicators allow complete program control.

### **SPECIFICATIONS**

perByte

| OF ECH ICATIONS                                        |           |           |           |

|--------------------------------------------------------|-----------|-----------|-----------|

| Name                                                   | RP04      | RP05      | RP06      |

| Туре                                                   | pack      | pack      | pack      |

| Formatted Capacity per Drive (bytes)                   | 88M       | 88M       | 176M      |

| Number of Drives per Control                           | 8         | 8         | 8         |

| Formatted Capacity<br>(on-line) per Control<br>(bytes) | 704M      | 704M      | 1408M     |

| Average Access Time                                    | 36 msec   | 36 msec   | 36 msec   |

| Average Transfer Time                                  | 1.24 used | 1.24 usec | 1.24 usec |

## RS03 and RS04 Fixed Disk System

**JULY 1976**

The RS03 and RS04 are fixed-head disk systems designed specifically for applications requiring fast, reliable, on-line storage. With an average access time of 8.5 milliseconds and a transfer rate of 4 microseconds per word, the RS03 and RS04 increase throughput substantially for timesharing applications which involve significant amounts of program swapping. Phase lock loop reading techniques and CRC error detection make these disk systems ideal for real-time data acquisition and control systems requiring a high level of reliability.

### **FEATURES**

### Speed

- 2/4 microseconds/word non-interleaved transfer RS04/RS03

- 4/8 microseconds/word interleaved transfer RS04/ RS03

- 8.5 milliseconds average access

- Real-time look-ahead

- Overlapped transfer

- Direct memory access

### Capacity

- RS03-512K 8-bit bytes/disk

- RS04-1024K 8-bit bytes/disk

### Reliability

- Phase lock loop clock system and modified frequency modulation recording

- Write checking

- · Prefilter and air filter for clean air

- · CRC error detection

### DESCRIPTION

The RS03 includes a controller and a rack-mounted RS03 fixed-head disk drive with a storage capacity of 256K 18-bit words. The RS04 includes a controller and a rack-mounted RS04 fixed-head disk drive with a storage capacity of 512K 18-bit words. The RS03 and RS04 are expandable by adding either RS03 or RS04 drives, up to a total of eight drives per controller. A single controller may have a mix of RS03 and RS04 drives. Two drives may be mounted in a single cabinet.

### Operation

Data is stored in blocks of 64 words for the RS03 and in blocks of 128 words for the RS04. The RS03 uses one read/write head at a time; the RS04 uses two heads in parallel. There are 64 heads for the RS03 and 128 heads for the RS04. The higher-capacity RS04 records information on both surfaces of the disk, whereas the RS03 uses only one surface. The number of sectors, 64, is the same, but the RS04 achieves double capacity by recording odd-numbered bits on one surface and evennumbered bits on the other surface.

Fast track-switching time permits "spiral" read/write from one track to the adjacent track in a single transfer operation. When the last sector on a track has been transferred, the disk automatically advances to the next track without any delay in the transfer rate. Up to 64K words can be transferred in a single operation.

The RSO3 and RSO4 also feature real-time look-ahead. This feature permits the program to monitor the current angular position of the disk and thereby minimize access time in a multidrive system when multiple requests are pending. Through the use of interrupts when comparing sectors, program time can be kept to a minimum. Except for the drive currently engaged in a data transfer, all drives can perform searches simultaneously.

#### Reliability

per Word

The RS03 and RS04 offer a high level of data reliability. They have been designed to provide a recoverable error rate of less than 1 in 10<sup>11</sup> bits read, and a nonrecoverable error rate of less than 1 in 10<sup>12</sup> bits transferred.

The use of a 16-bit Cyclic Redundancy Check (CRC) character per data block reduces the probability of undetected error to a negligible value. To ensure maximum reliability in the transmission of information between disk drive and control, a differential bus is used with parity generated and checked at the drive and at the control for both control and data transfers.

A phase lock loop clock system and MFM recording offer the latest in reliable reading and recording techniques. In addition, a write-check capability is used to verify data written on any disk without modifying either the disk or the memory data, and without the overhead of a programmed comparison between the original data in memory and the data written on the disk.

4 or 8/2 or 4

| SPECIFICATIONS        |            |

|-----------------------|------------|

| Name                  | RS03/RS04  |

| Туре                  | fixed head |

| Formatted Capacity    |            |

| per Drive (bytes)     | 512K/1024K |

| Number of Drives      |            |

| per Control           | 8          |

| Formatted Capacity    |            |

| (on-line) per         |            |

| Control (bytes)       | 4M/8M      |

| Average Access Time   | 8.5 ms     |

| Average Transfer Time |            |

770526

### PDP-11

## PC11/PR11 PAPER TAPE READER/PUNCH

**JULY 1976**

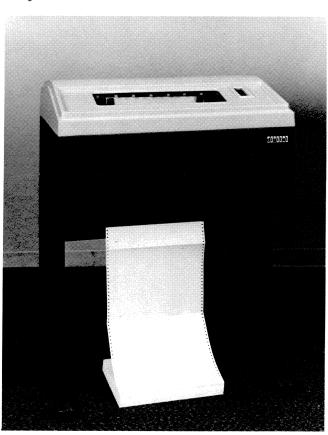

The PC11 high speed paper tape reader/punch features automatic fan-fold operation for easier, more reliable handling. It reads eight channel, unoiled perforated paper tape at 300 characters per second and punches at 50 characters per second. A similar system with read only capabilities (PR11) is also available.

### **FEATURES**

### Speed

- Read-300 characters/second

- Punch-50 characters/second

#### Efficiency

- Flexible program control because punch head is independent from the read head

- Automatic fan-fold operation

#### DESCRIPTION

The tape is read by a set of photodiodes which indicate the presence or absence of holes. The resulting signals are translated into logic levels representing 1's and 0's. Conversely, when punching tape, logic levels representing 1's and 0's are converted into punched-tape format.

Any information read or punched is parallel-transferred through the PC11 control. When an address is placed on the UNIBUS, the control decodes the address and determines if the reader or punch has been selected. If one of the four device register addresses is selected, the control also determines whether an input or an output operation should be performed. An input operation initiates when the processor transmits a command to the paper-tape reader status register. An output operation initiates when the processor transfers a byte to the paper-tape punch buffer register.

Both reader and punch can be operated independently of each other. Either device can be under direct program control (flag check), or they can be operated by interrupts.

The PC11 high-speed paper tape reader/punch control is a set of three modules that form a complete interface for the high-speed reader/punch (PC05) to the PDP-11 UNIBUS. The interface accepts data from the UNIBUS for direct transfer to the HSP data buffer. The interface also provides the gating of the HSR data buffer to the UNIBUS. All data transfers result from programmed commands received from the UNIBUS and are decoded within the interface logic. This logic can also request the UNIBUS and interrupt the processor program so that transfer operations can be performed.

The PR11 high-speed paper tape reader and control is also available for reader-only interfacing to the UNIBUS.

# **TA11 Magnetic Tape Cassette**

**JULY 1976**

The TA11 magnetic tape cassette system has been designed to provide extremely reliable, trouble-free performance. Features such as low density, wide track recording, heavy mylar tape, phase-encoded recording and cyclic redundancy error checking help eliminate tape failure and ensure accurate data recording and retrieval. At the same time this dual-drive unit is inexpensive enough to replace paper tape.

### **FEATURES**

### Speed

9.6 inches per second

### Capacity

• 92,000 characters

### **Human Engineering**

- Uses magnetic tape cassettes which are easy to insert and remove

- Media is easy to transport and store

### Reliability

- 1 MIL TAPE. Heavy mylar backing eliminates edge damage and resultant tape failure.

- REEL-TO-REEL DRIVE. Increases tape life. Only two driving elements. No pinch rollers, capstans, brakes, clutches, pulleys or belts.

- SINGLE TRACK RECORDING. Differentially balanced head eliminates external noise sensitivity. Low density and wide track recording ensure reliability.

- DC MOTORS. Linear servos provide precise, gentle tape acceleration and deceleration, eliminate stretching, and guarantee gap spacing.

- ERROR CHECKING CIRCUITS. 16-bit cyclic redundancy check.

- PHASE-ENCODED RECORDING. Read by sensitive, noise-immune peak detection circuits and phase lock loop.

- SERVICEABLE. Electronics, drives and power supply are easily accessible plug-in subassemblies.

- SOLID-CASTING DRIVE. All elements needed to control tape position, skew and motion are mounted on precision solid casting.

- MODIFIED HUB. Optimizes data capacity, simplifies loading.

- LEADER DETECTION. Optical, foolproof, failsafe.

- CASSETTES INTERCHANGEABLE. Assured by precision construction and frequency-independent read electronics.

### DESCRIPTION

### **Data Organization**

In the TA11 Cassette System, data is recorded on tape in a single bit-serial track of data. Since there is no prerecorded timing or format track (such as in DECtape), data must be sequentially recorded and retrieved as in conventional magnetic tape systems.

The cassette medium is an oxide coated tape with sections of clear leader (no oxide) appended to both ends. Data can not be recorded in these clear leader sections, but they identify BOT (beginning of tape) and EOT (end of tape). Placement of data onto the recordable region of the cassette tape is organized into units called files. Adjacent files are separated by file gaps, which are generated under software control. Each file consists of one or more blocks separated by block gaps. Block gaps are generated automatically. Each block consists of one or more bytes of data and two cyclic redundancy check (CRC) bytes. Under program control, the CRC bytes are appended when a block is written and checked when a block is read. Each byte consists of eight bits (no parity). The number of files, blocks per file, and bytes per block is unrestricted, except for tape capacity. Tape capacity is 92,000 bytes, minimum. This is reduced by 300 bytes per file gap and 46 bytes per block gap.

### **Controls & Indicators**

There are three manual controls on the tape drive. Each drive contains a separate REWIND pushbutton and a Power-On indicator. The Power ON/OFF toggle switch for the entire transport is located on the chassis rear panel. These manual controls and indicators perform the following functions:

**Rewind**-Pressing this momentary contact pushbutton on one of the two drives rewinds the tape on that drive, at high speed, to the Beginning-of-Tape (BOT) marker provided:

- a. a cassette is loaded.

- b. tape is not moving under program control.

Pressing this switch during a program controlled operation has no effect.

**Power ON/OFF**—Placing this switch in the ON position lights both Power-On indicators (located opposite the REWIND pushbuttons on the lower door of each drive) and activates the internal dc power supply. Conversely, placing this switch in the OFF position deactivates the power supply and turns off both Power-On indicators.

| Name                   | TA11     |

|------------------------|----------|

| Type                   | cassette |

| Formatted Capacity per |          |

| Reel (characters)      | 90,000   |

| Number of reels per    |          |

| Transport              | 2        |

| Number of Transports   |          |

| per Control            | 1        |

| Formatted Capacity     |          |

| (on-line) per Control  |          |

| (characters)           | 180K     |

| Average Transfer Time  |          |

| per Character          | 2 msec   |

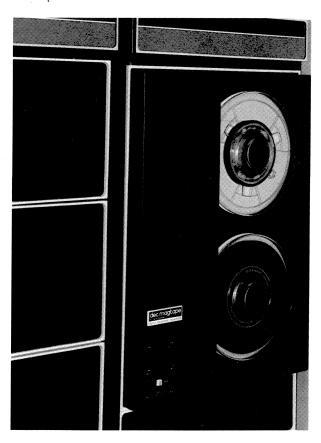

## TC11 DECtape System

**JULY 1976**

The TC11 DECtape system provides random access storage on 4 inch magnetic tape reels which can fit in a pocket. Data transfer speed is enhanced by bidirectional reading and writing of files and direct memory access. DECtape is engineered for high reliability as well as convenience and flexibility, e.g., redundant recording (each byte of data is recorded on two separate tracks) and parity checking on each block.

### **FEATURES**

### Speed

- 93  $\pm$  12 inches per second

- All operations are bidirectional

- Direct memory access

#### Capacity

147,968 16 bit words in blocks of 256 words each

### **Human Engineering**

- Small reels can be carried in a pocket

- Easy to mount and dismount

### Reliability

- No capstan or pinch roller, therefore longer tape life

- · Redundant recording of data

- Parity checking on each block

- Less than 1 transient error in 10<sup>10</sup> characters

- Insensitive to line voltage or frequency variation

- Tape is extremely tough

### **DESCRIPTION**

### Reliability

Low maintenance and high reliability is provided by the simple-designed TU56 transport mechanisms. The drives have no capstan or pinch rollers. Two drive motors control each tape transport. Each transport has a read/write head for information recording and playback on five channels of the tape. Each channel has two nonadjacent tracks with windings connected in series to provide complete redundancy. This redundancy provides exceptionally high reliability (less than one transient error in 1010 characters). Reliability is further enhanced by a hardware parity checking feature. This reliability permits use of DECtape without the closely controlled environment usually required for other forms of magnetic tape. Parity checking is performed for each block when read in either direction. Reliability is enhanced by using Mylar tape that is coated on both sides.

### Convenience

DECtape is unique—convenient pocket-sized reels are handy to carry and easy to mount and dismount. The reels permit convenient, separate filing and mailing of tape files. Each small 3.9 in. reel holds up to 147,968 16-bit words.

### **High-Speed Operation**

The bidirectional operation of DECtape provides highspeed access to stored program and data files. Reading, writing, searching, and updating may be conducted in either direction. Reading and writing is performed at the rate of 5000 16-bit words per second.

Data is recorded in blocks of 256 16-bit PDP-11 words. Each of 578 blocks is assigned a block number. The block number is recorded at both ends of each block; therefore, a block search may be performed in either direction. During a search operation, the current block number is updated in a control unit register for testing by the PDP-11 processor. This means that little processor overhead is required for search operations. Once the desired block is located, it may be updated "in place" and no recopying of subsequent blocks is required.

### **TC11 DECtape Control Unit**

The TC11 DECtape Control Unit buffers and controls information transfers between the PDP-11 control processor and the selected tape transport (one of eight). The processor controls unit selection, tape motion, direction and number of data transfers. The TC11 accepts and interprets these commands through five registers. These registers are assigned memory addresses and can be read or loaded under program control.

| Name                  | TC11    |

|-----------------------|---------|

| Туре                  | DECtape |

| Formatted Capacity    |         |

| per Reel (characters) | 295,000 |

| Number of Reels       |         |

| per Transport         | 2       |

| Number of Transports  |         |

| per Control           | 4       |

| Formatted Capacity    |         |

| (on-line) per         |         |

| Control (characters)  | 1M      |

| Average Transfer Time |         |

| per Character         | 10 μsec |

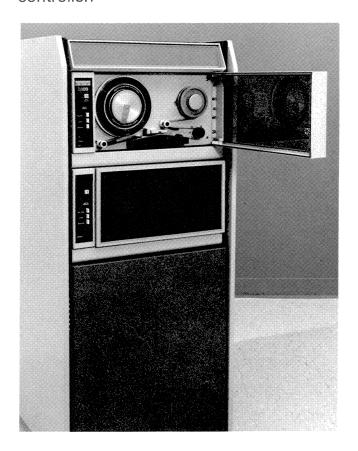

# **TU10W Magnetic Tape System**

**JULY 1976**

The TU10W is a low cost 9-or 7-track magnetic tape system that uses industry standard 200, 556, or 800-cpi NRZI recording format. From one to eight TU10W transports may be interfaced to a PDP-11 by a control unit. Each transport is mounted in a standard 19-inch cabinet. The TU10W sets a new standard for low cost and high quality for small computers.

### **FEATURES**

### Speed

• 45 inches per second

#### Capacity

17 million characters (1024 character blocks) on 7-or 9-track tape

### Reliability

- Read after write

- Vertical parity, LRC, CRC

- Long tape life because of vacuum column and servo controlled single capstan

- Write protect ring

### DESCRIPTION

### **High Performance**

Transfer rates as high as 36,000 characters per second; 45 ips at 800 bpi. Approximately 3 minutes rewind time for 2400-ft. reel.

### **Low Cost**

Most economical tape system in its performance class.

### **Industry Compatibility**

Compatibility with industry standard provides for efficient transfer of data between the PDP-11 and other computer systems; 7-channel at 200, 556, and 800 bpi; 9-channel at 800 bpi.

### Long Tape Life

The TU10W uses vacuum columns and a servo-controlled single capstan to control tape motion. The only contact with the oxide surface is at the magnetic head and a rolling contact on one low-friction, low-inertia bearing. Many other transports use dancer arms and pinch rollers that shorten tape life, cause errors, and require frequent adjustment.

### **High Reliability**

Dual-gap, read-after-write head checks parity, characterby-character. Longitudinal Redundancy Check automatically performed on both 7- and 9-channel units; Cyclic Redundancy Check automatically performed on 9-channel units. Ruggedized construction; shock mounted. Power failure interlocks prevent tape damage or data loss.

### **High Capacity**

$10\,{}^{1}\!\!/_{2}$  inch reel capacity permits up to 2400 feet of tape per transport.

### Expandable

Up to 8 transports may be driven by one TMB11 controller in any combination of 7- and 9-channel units. Thumbwheel indicator switch selects logical unit assignments.

### **SPECIFICATIONS**

TU10W Name Type magtape

Formatted Capacity

per Reel (characters) 20M

Number of Reels per Transport

1

**Number of Transports** per Control

Formatted Capacity

(on-line) per

Control (characters)

Average Transfer Time per Character

160M

8

$3\mu sec$

## TS03 Magnetic Tape

**JULY 1976**

The TS03 is a low-cost, 9-track magnetic tape system that uses industry-standard 800-bpi NZRI recording format. The basic system consists of a master tape drive, and a systems unit controller. A second tape drive can be added at the cost of the tape drive only, because the second (slave) drive uses the master drive's controller.

### **FEATURES**

### Speed

• 121/2 inches per second

### Capacity

- 7 inch reels

- 4 million characters (1024 byte blocks) per 9-track tape

### **Human Engineering**

- Small size

- Quiet because no cooling fans are needed

### Reliability

- Read after write to eliminate writing hard errors.

- Uses vertical parity, CRC, and LRC error detection codes.

- Linear drive reel serves to prolong tape life.

### Other

Low power consumption

### DESCRIPTION

The major features of the TS03 are high reliability, low cost, small size, and low power consumption. The major benefit is that, despite its low cost, the TS03 does not sacrifice reliability. It uses the same techniques to record data in the same manner as larger, more expensive transports, but it does this with a slower, extremely simple mechanism.

Cost savings result from small size because the TS03 frequently fits into existing cabinets. The TS03 occupies  $10\frac{1}{2}$ " of rack space and can fit into a processor cabinet with spare room left over for another subsystem. The controller occupies a systems unit in the processor expander box.

Small size also means lower power consumption because:

- There is no vacuum motor.

- The TS03 uses very low standby power-about the same as a medium-sized light bulb.

- It takes less power to drive the TS03's seven-inch diameter reels.

- Lower power consumption means a smaller load if back-up generator or batteries are used.

- Heat dissipation is so low that no cooling fans are needed

The absence of cooling fans also means that the TS03 is quiet—so quiet it cannot be heard running.

### Reliability

The TS03 is designed to read and write data to industry standards with high reliability. The calculated MTBF (Mean Time Between Failures) is 5,080 hours for the tape drive.

A unique feature of the TS03 eliminates the writing of hard errors on tape. If an error is detected in the readafter-write check, programming can cause the entire record to be rewritten. Hardware within the TS03 automatically senses that this is a retry and the readchecking margins are tightened up to ensure distinguishing between a transient error and a bad tape area. If the data passes on a second (or subsequent) pass, the written data is guaranteed to exceed the read thresholds. If there was a bad section of tape, the faulty record can be erased, then recorded correctly further down the tape.

| Name                                     | TS03           |

|------------------------------------------|----------------|

| Туре                                     | magtape        |

| Formatted Capacity per Reel (characters) | 5M             |

| Number of Reels<br>per Transport         | 1              |

| Number of Transports per Control         | 2              |

| Formatted Capacity (on-line) per         | 10M            |

| Control (characters)                     | TOW            |

| Average Transfer Time per Character      | <b>10</b> μsec |

## **TU16 Magnetic Tape Systems**

**JULY 1976**

The TU16 is a highly reliable 9-track tape storage system that uses industry compatible recording formats, with densities of 1600 and 800 bits per inch, selectable under control. Reading and writing are performed at 45 inches/second. Since the industry compatible format is used, data may be easily transferred between computers.

### **FEATURES**

### Speed

- 45 inches per second

- · Reading in reverse

### Capacity

- 26 million bytes (1024 byte blocks) per 9-track tape

- 1-8 drives per controller

### Reliability

- · Phase encoded on-the-fly error correction

- Read after write

- · On-line error and status reporting to CPU.

- Hardware diagnostic capability for off-line diagnostics and test.

- Long tape life because of vacuum column and servo controlled single capstan.

- Parity, LRC, CRC.

- Self clocking not dependent on precise skew control.

- Write protect ring.

- Runaway timer which stops tape if no read or write within a distance of 25 feet.

- Must be at least 12 characters in a block to be recognized as data

### **DESCRIPTION**

Reading can be performed while tape is moving in the forward or reverse direction, but writing occurs only in forward.

Tape motion is controlled by vacuum columns and a servo-controlled single capstan. Long tape life is possible because the only contact with the oxide surface is at the magnetic head and at a rolling contact on one low-friction, low-inertia bearing. The half-inch mylar-base tape is coated on one side with an iron oxide composition. The load and end points of the tape are marked by reflective strips which are detected by photo diodes. Approximately 10 feet of blank tape are wound on a reel, preceding the beginning of tape (BOT) and end of tape (EOT) strips. A gap of about three inches is left from the load point before writing can begin, with NRZI. With PE, an identification burst (IDB) is written in this gap.

There is a provision to prevent accidental writing on a particular tape reel. An industry-standard write-protect ring on the reel is sensed by the tape drive.

Parity is checked character-by-character when reading and writing on tape to verify the accuracy of data transfer. With NRZI, there is also a cyclic redundancy check (CRC) character generated or checked at the end of each record, plus a longitudinal parity check (LPC) character. If an error is detected, an error indication is made.

### Reliability

Data reliability of the TU16 tape system is enhanced by the 1600-bpi, phase-encoding, self-clocking feature which is not dependent on precise tape skew control. In addition, the 800-bpi NRZI mode includes a tight read-after-write check. The written data is checked to insure that it far surpasses the minimum allowable reading level.

Bad tape error problems are minimized by a "runaway timer" which allows the system to recover from bad tape sections on the reel. If no reading or writing is performed within a tape distance of approximately 25 feet, tape movement will stop and an error will be indicated. Data will not be acknowledged as comprising a data block unless there are at least 12 characters in the block.

### Upgrading

An NRZI 800-bpi-only tape system can be upgraded to have the 1600-bpi phase-encoded capability. An upgrade option is available for installation by DIGITAL Field Service at the customer's site.

| SPECIFICATIONS                           |         |

|------------------------------------------|---------|

| Name                                     | TU16    |

| Туре                                     | magtape |

| Formatted Capacity per Reel (characters) | 32M     |

| Number of Reels<br>per Transport         | 1       |

| Number of Transports<br>per Control      | 8       |

| Formatted Capacity<br>(on-line) per      |         |

| Control (characters)                     | 250M    |

| Average Transfer Time<br>per Character   | 1.4μsec |

### Photoelectric Card Readers

**JULY 1976**

The photoelectric card readers for the PDP-11 are designed to meet varying throughput requirements and data formats. All readers use the industry standard EIA card that has 80 columns and 12 zones (or rows). The CR11 and CM11 can process punched cards at 285 cards/minute, while the CD11 can process cards at up to 1200 cards/minute.

The CM11 can read cards marked with ordinary pencil or pen; it can also read a mixture of punched hole and mark sense within the same batch of cards or even within the same card.

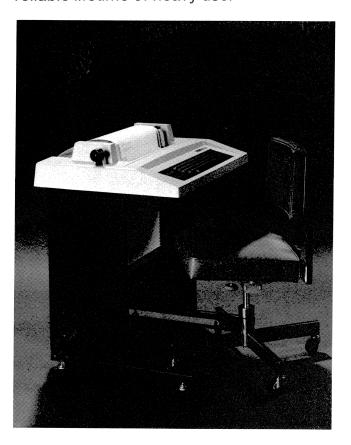

The CD11 has two versions: a tabletop unit with an input hopper capacity of 1000 cards that operates at 1000 cards/minute; and a free-standing floor model with a large 2250-card hopper that has a speed of 1200 cards/minute.

### **FEATURES**

### Speed

- CR11 and CM11-285 cards/minute.

- CD11 table-1000 cards/minute.

- CD11 floor-1200 cards/minute.

- All models achieve higher throughput through a continuous operation feature, i.e., cards may be loaded and unloaded during operation.

- The CD11 transfers data through direct memory access.

### Capacity

- CR11 and CM11-400 cards

- CD11 table=1000 cards

- CD11 floor-2250 cards

### **Human Engineering**

Quiet because of automatic shutdown switch.

### Reliability

- Fewer card jams because

- -higher tolerances

- -riffle air feed

- -vacuum picker

- -short card path

- -six attempts to read card before rejecting it

### **Flexibility**

Data formats selectable under program control

### DESCRIPTION

Reader design helps prevent card jams and keeps card wear to a minimum. Readers also have a high tolerance to cards that have been nicked, warped, bent or subjected to high humidity.

To keep cards from sticking together, the readers use a special "riffle air" feature. The bottom half inch of cards in the input hopper is subjected to a stream of air which separates the cards and air cushions them from the deck and from each other.

Cards entering the reader are selected through a vacuum picker. The picker and its associated throat block prevent the unit from accepting cards that have been stapled or taped together (unless such taping is on the leading edge). Because the card track is very short, only one card is in motion at any time. This minimizes the chances of cards jamming. Stoppages are also reduced since the reader automatically makes six attempts to process a card before rejecting it.

The read station uses infrared light-emitting diodes (LEDs) as its light source and phototransistors as its sensors. No adjustments are required during the ten-year life expectancy of the diodes.

Because card reader operation is flexible, cards can be loaded and unloaded while the reader is operating. A switch may be set to provide system blower shutdown or continual running after the last card has been read. Automatic shutdown reduces computer room noise level, and indicates that the card hopper is empty.

A control unit is included with the card reader.

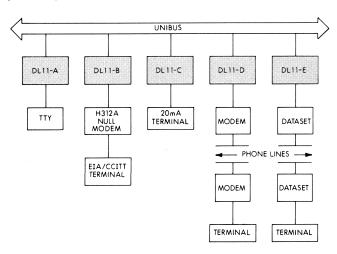

### **Data Formats**